### **Journal of Engineering Research**

Volume 7 Issue 5 This is a Special Issue from the Applied Innovative Research in Engineering Grand Challenges (AIRGEC) Conference, (AIRGEC 2023), Faculty of Engineering, Horus University, New Damietta, Egypt, 25-26 October 2023

Article 6

2023

# Experiential Learning in Computer Engineering using Basic Logic Design Circuits

Omer alkelany

Follow this and additional works at: https://digitalcommons.aaru.edu.jo/erjeng

### **Recommended Citation**

alkelany, Omer (2023) "Experiential Learning in Computer Engineering using Basic Logic Design Circuits," *Journal of Engineering Research*: Vol. 7: Iss. 5, Article 6.

Available at: https://digitalcommons.aaru.edu.jo/erjeng/vol7/iss5/6

This Article is brought to you for free and open access by Arab Journals Platform. It has been accepted for inclusion in Journal of Engineering Research by an authorized editor. The journal is hosted on Digital Commons, an Elsevier platform. For more information, please contact rakan@aaru.edu.jo, marah@aaru.edu.jo, u.murad@aaru.edu.jo.

Vol. 7 - No. 5, 2023

©Tanta University, Faculty of Engineering

ISSN: 2356-9441

https://erjeng.journals.ekb.eg/

## Experiential Learning in Computer Engineering using Basic Logic Design Circuits

Omer Alkelany<sup>1</sup>

<sup>1</sup>Acting Vice Dean for Graduate Studies, and Scientific Research, Horus University- Egypt - email: oalkelany@horus.edu.eg

Abstract- One of the main tracks of research is about Lowcost computing devices in engineering educations. This track face the problem that conventual methods are either too trivial demonstrative educational examples, or too abstracted that it hides away the necessary details students should learn, or too complex industry grade demonstrations. This research targets to utilize lost cost computing devices, and produce multiple stepby-step, educational components for university level. It relies on on the experiential learning methodology via generating multiple level educational components for Field Programmable Gate Array (FPGA) devices. Two basic design circuits were illustrated in this paper for two different FPGA boards, A comparison between conventional methods and proposed methods is also presented showing a favorable benefit, thus we disseminate this technique to researchers universities in the nation and abroad.

Keywords- Higher education enhancement, Technology in education, Field Programmable Gate Arrays (FPGA)s, Prototype Laboratory development.

#### Introduction

Field Programmable Gate Arrays, were introduced in 1985 by Xilinx, but at that time it offered very limited capability and was not so attractive to designers [1], After it was patented in 1992, it was used in a project funded by the US naval surface warfare department to develop reconfigurable logic computer components. From a few hundred configurable components, we have FPGAs that are capable of modeling millions of programmable gates. Its market share today is in the billions of US dollars.

Basic Logic gates are too many to list. But limited input gates, for example two input gates can be useful to illustrate how FPGAs work. Consider a table of two binary inputs, one output. It will have 4 rows listing the 4 possible input combinations (00, 01, 10, 11) ordered this way from top to bottom. Since any binary gate has only one output, the gate can be fully defined if the output is defined for all 4 input values. So, in this table, (i.e., the truth table), we need to assign the output by choosing either a '0' or a '1' in each of the 4 rows. For example, for the 2-input AND gate, the output must be assigned as 0,0,0,1, for the rows ordered from top to bottom. The 2-input OR gate the output assigned as 0,1,1,1, and the output of the XOR gate should be 0,1,1,0 and so on. Thus we can have up to 2<sup>4</sup> total different 2-input gates.

If we are given an integrated circuit that is capable to store these different output assignments in memory cells, and give us the ability to change them later, then we will be using an FPGA technology. The main concept of FPGA technology is its reconfigurable logic using Look-up-tables (LUT). FPGAs can use Static Random Access Memory (SRAM), to store LUT values for various output configurations we chose. Unlike Flash memories, SRAM is known that SRAMS are not vulnerable to wear-out for repeated writing [2]. Memories, i.e. SRAM are volatile, which means they need to stay powered to keep their contents. Even though this might be considered a disadvantage, but actually it allows us to erase contents quickly (i.e., eventually erasing all FPGA configurations) when power is disconnected. Of course, a copy of the configuration can be stored also on Flash memory, and reloaded the next time the power is connected to the FPGA. For beginner designers, educators use this feature as an advantage, since students don't have to worry too much about making design mistakes. Contents of the memory can be erased, and student can start again quickly, and safely.

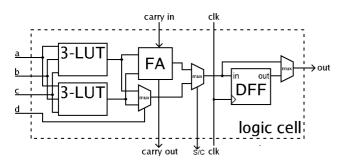

Figure 1 shows an example of a Configurable Logic Block CLB of 4 inputs, and two 3-input LUTs, Full-Adder (FA), sequential D-type flip flop (DFF), multiplexers (MUX) with select lines. One of the MUXs select lines is connected to the input d of the CLB, while the other is connected to the CLB sequential/combinational configuration choice to use or bypass the DFF correspondingly.

Actually, FPGA manufactures use SRAMs to allow configurable routing of wires as well. To imagine that, two intersecting wires can be set to connect or be insulated from each other by means of a binary gate to allow them so. Hence, the whole FPGA chip can be configured by knowing exactly what each "bit" needs to be in each wire crossing, and each LUT. This whole group of bits is called the configuration file. The term "Programmable" in FPGA name actually means loading this configuration file to its SRAM, so that it can operate as designed. It is unlike programming a computer in terms of serios of sequential instructions translated to binary code. Once the FPGA gets its configuration file loaded, it does not actually execute a program. It is implementing logic described by those LUTs and connections on its reconfigurable resources.

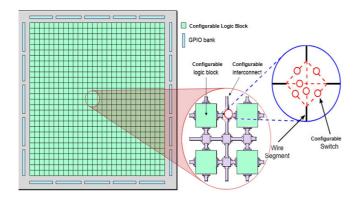

Figure 2 shows an example of a typical FPGA, with an array of CLBs, and reconfigurable interconnection wires. The modules of General-Purpose Input/Outputs (GPIO) are also of paramount importance, since they configure the mode of each of the pins of the chip to be input, output, bidirectional, buffered, etc. Modern FPGAs are based on the same concept, but they may also offer non-reconfigurable components, such as memory cells, microprocessors, input/output transceivers, and so on.

ISSN: 2356-9441

Figure 1: Example Configurable Logic Block of a generic FPGA

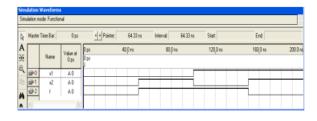

As mentioned before, digital logic function outputs can be fully defined when we state which binary values are assigned in a LUT format. A two-input LUT can have 16 configurations, but the values of the inputs will be used in any configuration to determine the output. With large number of CLBs, routing resources, and GPIO pins, computer aided design tools (such as Quartus II IDE for inter FPGAs) become a necessity to automate to translation of the design from any hardware description language to a binary output of FPGA configuration. These tools help not only in translating the given logic design into binary configuration file to the FPGA, but they are also very useful in simulating the design, performing time and power calculation, computing chip efficiency and resource utilization, etc. One of such features is shown in Figure 3, for performing a logic circuit simulation with a given test vector to a basic XOR logic gate.

Logic circuit designers are now equipped with sophisticated design tools, which make the FPGA a feasible choice for implementing, testing, evaluating multitude of integrated circuit components. Furthermore, FPGA technology allows designers to use already fabricated integrated circuits to implant logic circuits and changed them later. Thus, FPGAs become a perfect technology for educators who are involved in reconfigurable hardware design courses.

Figure 2: Illustration of a typical FPGA, with an array of CLBs, and reconfigurable interconnection wires via configurable switches

Figure 3: Example of functional simulation to XOR gate using FPGA design tools

Instructors using Experiential learning need to only show directions of how to accomplish a task, and not giving the learners all the details of how to take the route to the desired destination [3]. Thus, it makes learning an experience (i.e., not just perform an experiment) that moves beyond the classroom instruction and allows students the opportunity to draw conclusions, and being more involved in their own learning process.

Experiential Learning is thus considered as Learning by reflection on Doing [4-12]. It is not a new concept, and various philosophers stressed it in their teachings. It was conceptualized by Aristotle about Ethics as "for the things we have to learn before we can do them, we learn by doing them (first!)" [13]. However, in the 1970s, David A. Kolb developed a fundamental modern model of experiential learning [14]. According to Kolb, [15-16] the learner must be actively involved in the experience; reflect on the experience; analyze the outcomes; and perform decision making and problem-solving skills in order to use the new ideas gained from the prior experience. In this process, instructors to give constructive feedback to the learners, but they should not rush to provide the answer [17-19], especially when creative abilities are to be developed (critical thinking, design, synthesis, etc.), and particularly when there is not a single right answer. They will use their experience to judge or evaluate an outcome of a targeted component and share it with the learners [20-21].

Experiential learning was used in different fields of engineering education. For example [22], it was used via hardware emulators, and FPGA were used in latter stage of complex multi-part designs. Also, in 2020, two different comparative studies for experiential learning were done in two different universities in China, and New Zealand considering virtual reality applications, concluded that it enhances learning experience [23,25]. Furthermore, researchers investigated the incorporation of experiential learning at a Canadian university, in 2017, but they implemented it in a single engineering course, without FPGAs, and thus results were limited [25]. Recently, a research team in Horus University-Egypt adopted the use of FPGAs in experiential learning [26, 27].

#### II. BACKGROUND INFORMATION ABOUT MULTIPLEXERS

https://erjeng.journals.ekb.eg/ e ISSN: 2735-4873

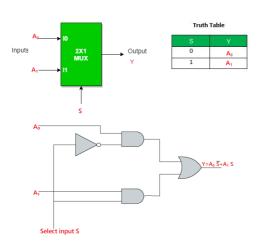

A multiplexor is a digital switch, which passes one of the many of its inputs to the output. It is sometimes called the pass/block module. In basic logic design courses, multiplexors of various input sizes become a perfect example to demonstrate the use of AND, OR, NOT gates. In its simplest form, it can be expressed with a single select line (S), two inputs, A<sub>0</sub>, A<sub>1</sub>, and an output Y. Figure 4 shows a simple logic circuit schematic for a two to one MUX.

Figure 4: A two to one Multiplexer: Block diagram, truth table, and logic circuit

In a typical Digital and Logic Design course, the instructor may wish to have his/her students experience the design of a multiplexer in various ways. Using logic simulations, lab premade modules, or discrete components (i.e., gates and wirings). Each of these alternatives have its drawbacks. More details on this in Section 4.

### III. EXPERIENTIAL LEARNING VIA A BASIC LOGIC DESIGN EXAMPLE USING MINI-FPGA BOARD

The author founded the Experiential Learning Research Lab in the Faculty of Engineering at Horus University-Egypt

Figure 5: The Experiential Learning Research Lab (EXL-Research) showing multiple stations

via funds made available both internally and externally. Figure 5 shows an angle of this lab, where stations are set to design different students experiences. [26, 27]

Of the acquired boards, is the Mini-FPGA board (EP2C5),

Figure 6: A Mini-FPGA Board Cyclone-II

shown in Figure 6. It has 4608 Logic Element (LE), which is similar to CLB mentioned in Section 1, 119,808 RAM bits, 13 embedded multipliers, 2 Phase locked Loops (PLL), and a 158 maximum user input/output pins [28].

For the EP2C5 board's simplicity, and limited on-board input/outputs, we used it to illustrate the implementation of a 2-input (i.e., A, B) XOR gate. In our design experience, we wanted to reflect the state of inputs A, B on LEDs, and show the output on another LED. Our goal is to give the students the experience to switch inputs and connect them to different voltage pins, and see the variations on LEDs, during their basic FPGA design experience stage.

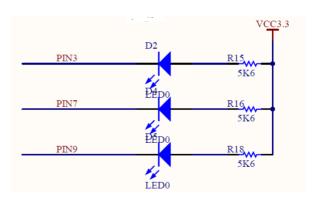

The Mini-FPGA board EP2C5 shown in Figure 6, has three integrated LEDs on the board, namely D2, D4, D5, on the upper left edge of the board shown in Figure 6. These LEDs are connected to the Cyclone II pins PIN\_3, PIN\_7, PIN\_9 on the EP2C5 board. The EP2C5 board has active low LEDs as shown in Figure 7. It also has a user defined push button is connected to PIN\_144 of the EP2C5 board. For the two-input XOR to work properly we will also need inputs for the XOR, so we used pins 141, 137. A pair of jumper wires were used

Figure 7: Active low LED connections in the Mini-FPGA Board

ISSN: 2356-9441

to connect GND or binary level '0' or VCC for binary level '1' to the XOR inputs.

module xor2 (x1,x2,O1,O2,O3);

input x1; //pin\_141

input x2; //pin\_139

output O1,O2,O3;

//assign O1=x1^1; //inverter

assign O1=!x1; //active low LED D2, pin\_3

assign O2=!x2; //active low LED D4, pin\_7

assign O3=!(x1^x2); //active low LED D5, pin\_9

endmodule

Figure 8: Verilog code for the XOR illustration

We used Verilog HDL to model the XOR gate, for illustration purposes. In Verilog, a module keyword is used to define its name, and parameters, which must be declared as either inputs or outputs. So, we defined x1, x2 as inputs, and O1, O2, O3 as outputs. Since the LEDs are active low, we designed the logic with activity conversion. The Verilog standard operators include the '!' for not, and '^' for XOR. So, we used a NOT operator to reverse the logic of inputs, and

Figure 9: Working project for the basic XOR circuit

make it match LED states, that is GND on x1 will keep the LED off, while VCC will light the corresponding LED. Figure 8 shows the full listing of the XOR basic illustration project. Test after the '//' is just for explanations.

Consequently, students will need to compile the code in Figure 8, establish a JTAG-USB connection to transfer the binary configuration file from the computer to the Mini-FPGA board. Student will also be asked to experience what happens when the jumper wires for x1, x2 are switched from GND to VCC. Figure 9 shows an instance of the working XOR project on the EP2C5 board.

Similarly, to illustrate the implementation of the 2-1 multiplexer, mentioned in Section 2, we will only need to use 3 inputs and one output of the FPGA. Specifically, we need input pins for A<sub>0</sub>, A<sub>1</sub>, and S, as well as output pin for Y. We also need LEDs to show the state of the two inputs A<sub>0</sub>, A<sub>1</sub> and the Output Y. Since the goal is to have a design experience, we switch the student to work on a more advanced FPGA board, the Altera DE2, shown in Figure 10 [29].

Figure 10: More sophisticated Altera DE2 board

Figure 11 shows a similar listing to represent the 2:1 MUX introduced earlier in Section 2. Recall how in Figure 4 we had different ways to model such MUX. Using a truth table, logic circuit, or logic equation. The simplest of all three is the use of logic equation. And since Verilog based design tools can directly translate logic equations to FPGA LUTs, we find it provident that students learn such technique by experience.

```

module mux2to1 (A0,A1,S,Y);

input A0,A1,S;

output Y;

assign Y=(A0 \& !S) | (A1 \& s);

endmodule

```

Figure 11: Verilog code for the 2:1 MUX illustration

### alkelany: Experiential Learning in Computer Engineering using Basic Logic D

©Tanta University, Faculty of Engineering https://erjeng.journals.ekb.eg/

ISSN: 2356-9441

Furthermore, only the pin assignments file will NOT be given to the student, and they will have to learn how to choose the proper pins to connect to the FPGA chip, in order to test the 2:1 Mux. They will only be given instructions to where they can find valid pin table [30].

Based on a Cyclone II FPGA boards, the instructor may further challenge the students by projects of medium to high complexities. Examples include time multiplexing/switching between inputs of keyboard, or keypad, interfacing to complex peripherals such as analog to digital/digital to analog converts, cameras or LCDs. Thus, students will need to use more capabilities of the FPGA design tools. Also, for advanced courses, the same project can be extended to send the outputs to a network interface, thus using a web browser, and a microprocessor on the FPGA chip and so on. In those later experiences, students will need to learn more about Hardware Description Languages (HDL), such as Verilog or VHDL together with Schematic editors, in-chip logic analyzers, functional simulations, and timing simulations.

### FPGA BASED EXPERIENTIAL LEARNING COMPARISON WITH CONVENTIONAL METHODS

Conventual ways to implement basic logic circuits include:

- Logic simulation

- Discrete component implementations

- Ready off-the-shelf logic blocks

Int the following we list advantages and disadvantages of these choices as they compare with

Modern, FPGA based logic circuit implementations

Logic simulation: This is typically a computer-based simulation of the logic circuits (such as Logisim, Modalism, etc.). Although very useful to illustrate teaching concepts, but they fail to give the necessary physical experiences, and students may still find it not convincing that their design will actually work.

Discrete component implementations: This is straight forward buy, and try approach. Usually, students are asked to acquire parts on their own, and build the circuit. Most of the time, due to lack of prior experiences, students break many parts, and may get frustrated from having to buy more parts to replace failed ones. Also, it requires a very thorough attention to details of all wirings, which can be sometimes too time consuming and also frustrating.

Ready off-the-shelf logic blocks: This tries to remedy the problems of previous choice, but for its simplicity, fails to give the student the proper hardware experiences of industrial implementation technology.

Furthermore, none of the implementation methods used above are actually used in the computer logic design industry today.

FPGA technologies have reached a maturity level that is used in industry and can be also used in multi level (i.e., basic to complex) design circuits.

#### **CONCLUSIONS**

In this paper, the we presented two basic logic circuit design experiences for the experiential learning pedagogy. Detailed step by step illustrations were give, so that instructors can use it to duplicate the experiences and benefit from them. Furthermore, we compared such developed experiences with conventual methods, showing that experience learning, even in its basic form resolves the problems found in traditional teaching.

### VI. ACKNOWLEDGMENT:

**Funding:** This research is supported by the Egyptian Science Technology Development Fund-research proposal #45945 for the years 2022-2024.

#### **Conflicts of Interest:**

All authors declare that they have no conflict of interest regarding this research paper and that they comply with research ethics.

### REFERENCES

- [1] -, "FPGA Design A Brief History," July, 18th, 2010, https://www.enventure.com/blog/fpga-design-a-brief-history/, accessed August, 2023.

- [2] Kevin Wible, "What is an FPGA and how does it Work?," https://www.cardinalpeak.com/blog/curious-about-what-an-fpgais-and-how-it-actually-works, accessed August, 2023.

- [3] Hawtrey, Kim. "Using Experiential Learning Techniques". Journal of Economic Education, volume 38, issue. 2, pp. 143-152,

- [4] Felicia, Patrick. Handbook of Research on Improving Learning and Motivation. ISBN 978-1609604967, 2011.

- [5] MIT Sloan Management, "Action Learning How does it work in practice?", Why back mission site, 2016.

- [6] -, The Power of Experiential Learning, 4-H Cooperative Curriculum System. 2016.

- -, The Out of Eden Walk: An Experiential Learning Journey from the Virtual to the Real, http://www.edutopia.org/blog/out-ofeden-experiential-learning-homa-tavangar, January 3, 2014. Retrieved 2020.

- [8] MIT Sloan, Action Learning How does it work in practice? http://mitsloan.mit.edu/mba/program-components/hands-onlearning/, retrieved 2021.

- The Power of Experiential Learning, 4-H Cooperative Curriculum System, http://njaes.rutgers.edu/learnbydoing/ retrieved 2020.

- [ 10] Beard, Colin (2010). The Experiential Learning Toolkit: Blending Practice with Concepts. p. 20. ISBN 9780749459345, https://books.google.com/books?id=DAhYlaZhRI8C&pg=PA20 retrieved 2020.

- [ 11] Itin, C. M., Reasserting the Philosophy of Experiential Education as a Vehicle for Change in the 21st Century. The Journal of Physical Education 22(2), p. 91-98, 1999.

- [ 12] Breunig, Mary C., "Teaching Dewey's Experience and Education Experientially". In Stremba, Bob; Bisson, Christian A. (eds.). Teaching Adventure Education Theory: Best Practices. p. 122. ISBN 9780736071260, 2009.

- [13] Nicomachean Ethics, Aristotle, Book 2, D.P. Chase translation, 1911.

### Journal of Engineering Research, Vol. 7 [2023], Iss. 5, Art. 6

©Tanta University, Faculty of Engineering

https://erjeng.journals.ekb.eg/

[ 14] Dixon, Nancy M.; Adams, Doris E.; Cullins, Richard. "Learning Style". Assessment, Development, and Measurement. p. 41. ISBN 9781562860493, 1997.

ISSN: 2356-9441

- [ 15] Kolb, D., Experiential Learning: experience as the source of learning and development. Englewood Cliffs, NJ: Prentice Hall. p. 21, 1984.

- [ 16] Kolb, D., Experiential Learning, http://www2.le.ac.uk/departments/gradschool/training/resources/ teaching/theories/kolb, 2012.

- [ 17] Merriam, S. B., Caffarella, R. S., & Baumgartner, L. M., Learning in adulthood: a comprehensive guide. San Francisco: John Wiley & Sons, Inc., 2007.

- [ 18] Moon, J., A Handbook of Reflective and Experiential Learning: Theory and Practice. London: Routledge Falmer. p. 126., 2004.

- [19] Kolb, D, Experiential Learning as the Science of Learning and Development. Englewood Cliffs, NJ: Prentice Hall.1984.

- [20] Chickering, A., Experience and Learning. New York: Change Magazine Press. p. 63., 1977.

- [21] Hutton, M., Learning from action: a conceptual framework, in S. Warner Weil and M. McGill (eds) Making Sense of Experiential Learning. Milton Keynes: SRHE/Open University Press. pp. 50– 9, p. 51, 1980.

- [22] J. O. Hamblen, H. L. Owen, S. Yalamanchili and Binh Dao, "An undergraduate computer engineering rapid systems prototyping design laboratory," in IEEE Transactions on Education, vol. 42, no. 1, pp. 8-14, doi: 10.1109/13.746325, 1999.

- [ 23] C. Zhou, H. Li and Y. Bian, "Identifying the Optimal 3D Display Technology for Hands-On Virtual Experiential Learning: A Comparison Study," in IEEE Access, vol. 8, pp. 73791-73803, doi: 10.1109/ACCESS.2020.2988678, 2020.

- [ 24] E. Rho, K. Chan, E. J. Varoy and N. Giacaman, "An Experiential Learning Approach to Learning Manual Communication Through a Virtual Reality Environment," in IEEE Transactions on Learning Technologies, vol. 13, no. 3, pp. 477-490, 1, doi: 10.1109/TLT.2020.2988523, 2020.

- [25] Hajshir Mohammadi, "Incorporating Experiential Learning in Engineering Courses," in IEEE Communications Magazine, vol. 55, no. 11, pp. 166-169, doi: 10.1109/MCOM.2017.1700373, 2017.

- [ 26] Omer Alkelany, Hatem Khater, Mohamed Kamal, Hosam E. Mostafa, "Preliminary Evaluation of Experiential Learning in Engineering Pedagogy for Undergraduate Students Learning Logic Design Concepts" Proceedings of the First International Conference on Engineering Solutions toward Sustainable Development (ESSD-2023).

- [27] Omer Alkelany, Hatem Khater, Mohamed Kamal, Hosam E. Mostafa, "Survey and Evaluation of Applied Modern Engineering Pedagogy" Proceedings of the First International Conference on Engineering Solutions toward Sustainable Development (ESSD-2023).

- [ 28] -, Data sheet for Altera Cyclone II family, https://datasheet.octopart.com/EP2C5T144C8-Altera-datasheet-7627975.pdf, pages 7-8 of 168, accessed August 2023

- [29] Terasic, Altera DE2 board: <a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=30,Accessed">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=30,Accessed</a> August 2023

- [ 30] Altera DE2 Pin Table: <a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3</a>

<a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3</a>

<a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3</a>

<a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3</a>

<a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3">https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=53&No=3</a>

<a href="https://www.terasic.com.tw/cgi-bin/page/archive.pl?">https://www.terasic.com.tw/cgi-bin/page/archive.pl?</a>

<a href="https:/