### **Journal of Engineering Research**

Volume 8 Issue 4 *issue 4*

Article 12

2024

# Enhancing Radiation Performance of a 0.18 µm CMOS 60 GHz On-chip Double-Slot Vivaldi Antenna

Elsayed Ibrahim Elsaidy Mr.

Faculty of Engineering Tanta University, Tanta, Egypt., s.elsaidy@f-eng.tanta.edu.eg

Amr H. Hussein Prof.Dr.

Faculty of Engineering Tanta University, Tanta, Egypt., amr.abdallah@f-eng.tanta.edu.eg

Mustafa M. Abd Elnaby Prof. Dr.

Faculty of Engineering Tanta University, Tanta, Egypt., mnaby@f-eng.tanta.edu.eg

Follow this and additional works at: https://digitalcommons.aaru.edu.jo/erjeng

Part of the Electromagnetics and Photonics Commons, and the Electronic Devices and Semiconductor Manufacturing Commons

#### **Recommended Citation**

Elsaidy, Elsayed Ibrahim Mr.; Hussein, Amr H. Prof.Dr.; and Abd Elnaby, Mustafa M. Prof. Dr. (2024) "Enhancing Radiation Performance of a 0.18 µm CMOS 60 GHz On-chip Double-Slot Vivaldi Antenna," *Journal of Engineering Research*: Vol. 8: Iss. 4, Article 12.

Available at: https://digitalcommons.aaru.edu.jo/erjeng/vol8/iss4/12

This Article is brought to you for free and open access by Arab Journals Platform. It has been accepted for inclusion in Journal of Engineering Research by an authorized editor. The journal is hosted on Digital Commons, an Elsevier platform. For more information, please contact marah@aaru.edu.jo,rakan@aaru.edu.jo.

Journal of Engineering Research (JER)

©Tanta University, Faculty of Engineering

ISSN: 2356-9441

Vol. 8 - No. 4, 2024

eISSN: 2735-4873

# Enhancing Radiation Performance of a 0.18 µm CMOS 60 GHz On-chip Double-Slot Vivaldi Antenna

Elsayed Elsaidy<sup>1</sup>, Amr H. Hussein<sup>1,2</sup>, and Mustafa M. Abd Elnaby<sup>1</sup>

<sup>1</sup>Electronics and Electrical Communications Engineering Dept., Faculty of Engineering Tanta University, Tanta, Egypt. <sup>2</sup>Electronics and Communications Engineering Dept., Faculty of Engineering, Horus University, New Damietta, Egypt. s.elsaidy@f-eng.tanta.edu.eg, amr.abdallah@f-eng.tanta.edu.eg, mnaby@f-eng.tanta.edu.eg

Abstract- This paper presents the design of a 60-GHz double-slot Vivaldi antenna (DSVA) using standard 0.18 µm CMOS technology. The antenna's two slots are uniformly excited in both amplitude and phase by a coplanar waveguide (CPW) power divider. A double-Y balun feeding structure is also used to transition from the CPW to the coplanar slot line (CPS). Two techniques are investigated to enhance the antenna's radiation characteristics. The first technique involves incorporating equal corrugations along the edges of the flare aperture, resulting in a significant gain enhancement of 0.9 dBi and an improvement in radiation efficiency by 7%. The second technique entails the construction of a planar arc reflector to suppress the back lobe, further enhancing gain by 0.7 dBi and radiation efficiency by 6%. The overall antenna dimensions are compact, measuring 870 µm × 960 µm. It exhibits an end-fire radiation pattern with a simulated peak gain and radiation efficiency of + 0.4 dBi and 38%, respectively. Furthermore, the measured reflection coefficient indicates that the impedance bandwidth of the DSVA spans from 50 to 70 GHz.

Keywords: Vivaldi antenna, 0.18 µm CMOS technology, Balun, CPW Power divider.

#### I. INTRODUCTION

The millimeter-wave band, especially the unlicensed 60 GHz band with a 7 GHz bandwidth (57-64 GHz), has recently become a significant research focus due to the rising congestion in the lower-frequency spectrum. This frequency band is highly suitable for high-speed, short-range communication. It is ideal for advanced applications such as 5G, the Internet of Things (IoT), and wireless personal area networks (WPANs) [1, 2]. Nevertheless, signals at 60 GHz are subject to substantial atmospheric absorption, restricting their transmission range [3].

On-chip antennas (AoCs) integrated into System-on-Chip (SoC) technology offer significant advantages, including miniaturization, cost reduction, low power consumption, and simplified packaging by eliminating lossy bond wires. However, they face challenges such as performance degradation due to the silicon substrate's low resistivity (~10  $\Omega\cdot$ cm) and high permittivity (11.9), which absorb electromagnetic waves and reduce efficiency. Additionally, mutual coupling in 5G applications can degrade performance, and accurate measurement is difficult due to integration with other on-chip components. Therefore,

innovative design solutions are required to fully harness the potential of AoCs [4, 5].

Numerous researchers have explored techniques to enhance AoCs' performance, including substrate postprocessing methods such as micromachining and ion implantation to create high-resistivity substrates [6, 7]. While these techniques improve antenna radiation, they often reduce system-level integration and increase overall costs. Consequently, antennas must be fabricated using the standard CMOS process to ensure substrate compatibility and cost-effectiveness. Recent research focuses on utilizing various embedded reflecting surfaces, such as Artificial Magnetic Conductors (AMCs), to enhance AoC radiation [8-11]. AMCs electromagnetically shield the AoC from the lossy CMOS substrate due to their reflection characteristics. Although AMC layers can be implemented using the existing metal layers of the CMOS stack-up, making them cost-effective, AMC-based on-chip antennas typically have lower gains than other enhancement techniques.

Vivaldi antennas, a type of end-fire antenna, are gaining popularity in radar and array configurations due to their high gain, wide bandwidth, and simple structure [12]. However, the Tapered Slot Antenna (TSA), a type of Vivaldi antenna, faces a significant design trade-off. For better radiation characteristics, the TSA's width should be greater than  $\lambda/2$ , where  $\lambda$  is the wavelength. This requirement reduces the compactness of the antenna, which is crucial for practical applications such as MM-Wave imaging arrays. A few studies have proposed Vivaldi antennas on 0.18 µm CMOS technology, but many results have focused on Yagi antennas, examining their geometry, characteristics, and applicationspecific designs. Earlier 60-GHz Yagi and Vivaldi antenna designs employing CMOS technology have faced limited applications due to their low radiation efficiency, which typically ranges between 5% and 24% [5, 13-17].

This paper presents the design of a 60-GHz CMOS DSVA using 0.18-µm CMOS technology. The primary objective is to investigate techniques for enhancing radiation properties. Firstly, equal corrugations are etched on the edges to concentrate surface current towards the inner edge of the tapered slots, which enhances antenna gain and radiation efficiency. Secondly, a planar arc reflector is constructed to

eISSN: 2735-4873

reduce backside radiation, further improving antenna gain and radiation efficiency. Additionally, the double-slot structure ensures a more uniform distribution of the aperture field at the antenna's end, resulting in higher gain than a single-slot Vivaldi antenna (SSVA) of the same size. The paper is structured as follows: Section II provides details of the proposed 0.18  $\mu$ m CMOS 60-GHz DSVA design, Section III presents the results and compares them with previous work, and Section IV offers the paper's conclusion.

#### II. ANTENNA DESIGN

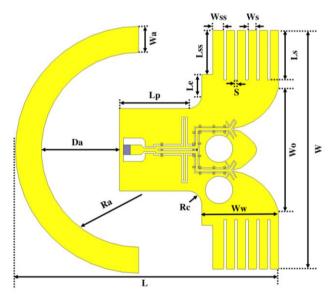

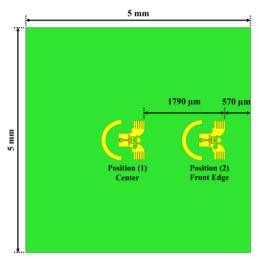

The DSVA is designed using 0.18  $\mu$ m CMOS technology with six metal layers (M1 to M6). The antenna without the arc reflector is located on the top metal layer (M6), while the ground plane is on the bottom layer (M1), minimizing conduction losses and enhancing performance. An arc reflector is also constructed between M1 and M6 using metal vias placed behind the antenna. The configuration of the proposed DSVA is depicted in Fig. 1. The antenna is designed on a 5 mm  $\times$  5 mm substrate, a typical substrate area for a SoC. The tapered slots of the DSVA are created using two-slot lines in an exponentially tapered structure.

Fig. 1. Structure of the proposed DSVA.

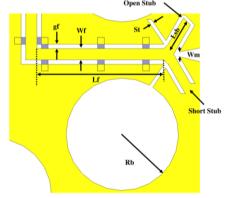

Fig. 2. Structure of the double-Y balun.

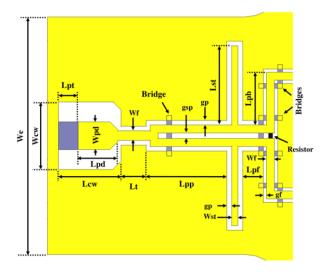

Fig. 3. Structure of the CPW power divider.

The CPW feeding technique connects the Ground Signal Ground (GSG) probe used in the measurement phase. This is achieved using CPW to CPS transitions to feed the antenna slots. A double-Y balun is a CPW to CPS transition that does not have any inherent bandwidth limitation [18]. Illustrated in Fig. 2, a double-Y balun, derived from a six-port double-Y junction, converts signals between balanced and unbalanced lines with minimal loss. Terminating specific ports with open and short circuits achieves the necessary antiphase reflection coefficients. The pad dimensions are designed to be 50 Ohms, and the input and output impedances of the double-Y balun are also chosen to be 50 Ohms. Additionally, a CPW power divider is employed to ensure that the two slots of the DSVA are excited in uniform amplitude and phase, as shown in Fig. 3 [19]. In the CPW power divider, the isolation resistor with a value of 100 Ohms prevents unwanted signal coupling between output ports, ensuring high isolation, minimizing signal distortion, and improving circuit performance. Besides, bridges in the CPW circuit maintain signal integrity by suppressing unwanted slot line mode propagation and ensuring cleaner signal transmission [20, 21].

The Vivaldi antenna is often preferred due to its wide operating bandwidth. However, as the frequency increases, various issues degrade its radiation characteristics. One significant problem is the unwanted radiation from currents traveling along the flare termination sections. This radiation leads to gain reduction, side lobes, and pattern distortion but can be suppressed by corrugating the termination sections. The corrugations are incorporated along the edges of the Vivaldi antenna's structure to address this problem [1, 22]. In DSVA, these corrugations enhance radiation the performance by introducing inductance and capacitance, altering the current distribution along the edges. The corrugation structure effectively acts as a high-impedance region, concentrating the surface current toward the inner edge of the tapered slots. This results in an improved front-

eISSN: 2735-4873

to-back ratio, reduced backward radiation, enhanced directivity, and a more focused radiation pattern in the endfire direction, significantly improving gain across a wide frequency range. Additionally, the corrugations increase the antenna's effective length, making the DSVA more compact. Furthermore, a planar arc reflector is strategically placed behind the antenna along its axis. This reflector effectively suppresses the back lobe, significantly enhancing the antenna's radiation characteristics.

#### III. RESULTS AND DISCUSSION

In this study, electromagnetic (EM) simulations were conducted using the ANSYS High-Frequency Structure Simulator (HFSS®). As listed in Table I, the antenna parameters were optimized through parametric studies and optimization techniques.

#### A. Effect of antenna position on its performance

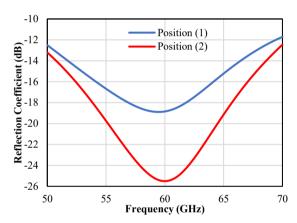

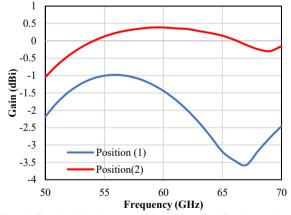

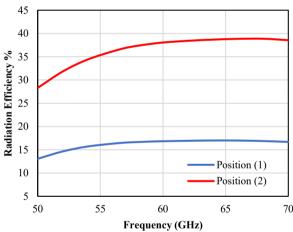

The performance of an AoC is significantly influenced by its position on the substrate [5, 17]. Antennas near the edge perform better than those at the center due to reduced substrate losses and better coupling with the surrounding air. When optimally positioned, the antenna benefits from a smaller lossy substrate area in front of it, enhancing radiation efficiency and gain. In contrast, a centrally located antenna may suffer from increased losses due to the larger substrate area it interacts with, leading to lower efficiency and gain. Therefore, the optimal position for the proposed DSVA on the substrate is position (2), as illustrated in Fig. 4. When the DSVA is shifted to the right or left along the substrate edge, it maintains its performance. However, the maximum radiation pattern is slightly deflected due to substrate asymmetry around the DSVA. The comparison of the optimal performance location (Position (2)) and the central location (Position (1)) is depicted in Fig. 5, Fig. 6, and Fig. 7. Both antennas achieve matching at the desired bandwidth around 60 GHz. The total realized gain and radiation efficiency at position (2) surpass those at position (1) across the operational frequency band. Specifically, at 60 GHz, the gain increases from -1.4 dBi to + 0.4 dBi, and the radiation efficiency improves from 16.8 % to 38 %. Moreover, the front-to-back ratio decreases from 7.6 dB to 4.7 dB when the antenna is relocated from position (1) to position (2).

Table I: Optimized geometrical parameters of proposed DSVA

| W   | L   | Wo   | Ww  | Ls  | Ws  | S   | Wss  | Lss     |

|-----|-----|------|-----|-----|-----|-----|------|---------|

| 870 | 960 | 450  | 280 | 210 | 30  | 10  | 40   | 159.5   |

| Le  | Lp  | Da   | Ra  | Wa  | Rc  | We  | Wcw  | Lpt     |

| 75  | 250 | 285  | 450 | 95  | 50  | 300 | 85   | 25      |

| Lcw | Lpd | Wpd  | Wf  | Lt  | Lpp | gp  | gsp  | Wst     |

| 79  | 50  | 35   | 12  | 32  | 148 | 6   | 7    | 8       |

| Lst | Lpf | Lpb  | gf  | Lf  | Rb  | St  | Lsb  | Wm      |

| 100 | 26  | 66.5 | 4   | 113 | 50  | 3.7 | 29.9 | 4.5     |

| Rb  |     |      |     |     |     |     | Ur   | its: μm |

| 50  |     |      |     |     |     |     |      |         |

Fig. 4. Proposed DSVA design in Positions (1) and (2).

Fig. 5. Simulated reflection coefficient versus frequency for Position (1) and Position (2).

Fig. 6. Simulated gain versus frequency for Position (1) and Position (2).

#### B. Performance Enhancement Techniques

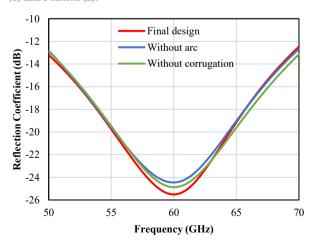

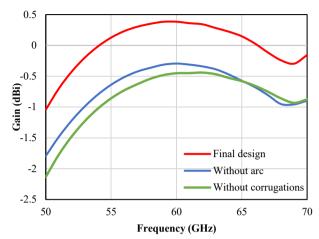

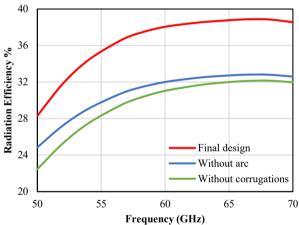

The effect of equal corrugations and planar arc on the proposed DSVA performance was studied at the optimum location (Position (2)). The antenna parameters were

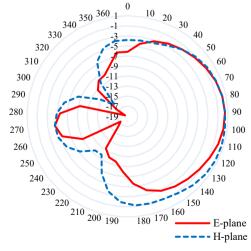

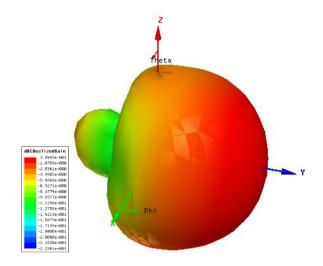

adjusted to operate at the same center frequency of 60 GHz. The simulated curves of the reflection coefficient, the realized gain, and the efficiency are shown in Fig. 8, Fig. 9, and Fig. 10, respectively. For all configurations, the reflection coefficients are below - 24 dB at 60 GHz. It can be observed that the effect of the equal rectangular corrugations is significant, resulting in a gain enhancement of 0.9 dBi and an improvement in radiation efficiency by 7 %. Furthermore, the planar arc reflector positively impacts the antenna's performance, improving the gain and radiation efficiency by 0.7 dBi and 6 %, respectively. As depicted in Fig. 8, the final design of the proposed DSVA operates at 60 GHz, covering a bandwidth of over 20 GHz, from 50 GHz to beyond 70 GHz. This indicates that the ultrawideband characteristic of the Vivaldi antenna is well-maintained after replacing the SSVA with the proposed DSVA. Due to the combined effects of both the corrugations and planar arc reflector, the gain and efficiency of the antenna are significantly increased in the end-fire direction to + 0.4 dBi and 38 %, as shown in Fig. 9 and Fig. 10, respectively. The proposed DSVA also features compact dimensions, measuring 870 μm × 960 μm. Fig. 11 and Fig. 12 illustrate the simulated 2-D patterns in

Fig. 7. Simulated radiation efficiency versus frequency for Position (1) and Position (2).

Fig. 8. Simulated reflection coefficient versus frequency for DSVA.

the E- and H- planes and the simulated 3-D radiation pattern at 60 GHz for the final proposed DSVA design.

Fig. 9. Simulated gain versus frequency for DSVA.

Fig. 10. Simulated radiation efficiency versus frequency for DSVA.

Fig. 11. Simulated 2-D patterns for DSVA at 60 GHz.

eISSN: 2735-4873

#### C. Measurement Results

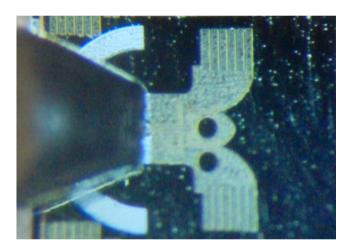

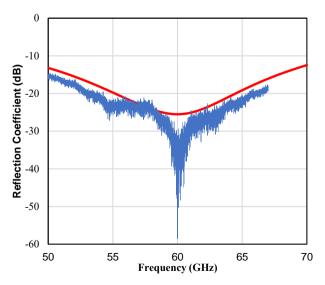

The DSVA on-chip is fabricated using TSMC  $0.18~\mu m$  CMOS technology. The photograph of the fabricated AoC is presented in Fig. 13. Measurements are conducted using an Agilent E8361C PNA, a manual probe station, and a Microtech 100  $\mu m$  pitch Infinity® probe. A comparative analysis of the measured and simulated reflection coefficient parameters of the fabricated AoC on a 5 mm by 5 mm substrate is depicted in Fig. 14. The measured reflection coefficient results demonstrate matching within the 50 GHz to 67 GHz frequency range, corresponding to the maximum measurable frequency of the available PNA. The reflection coefficient measurements exhibit a wider bandwidth, indicating a lower quality factor. This broader bandwidth is attributed to additional losses not accounted for in the simulations.

Compared to the SSVA (with a size of 930  $\mu m$  x 785  $\mu m$ ) proposed in [17], the DSVA can improve the performance better and in a wider band. The Simulated gain and efficiency for 60 GHz of the SSVA in [17] are 0.4 dBi and 32%, respectively, whereas those of the proposed DSVA in this paper are + 0.4 dBi and 38%, respectively. Moreover, the DSVA's structure area is approximately the same as the SSVA in [17]. Finally, Table II presents a performance comparison of related on-chip CMOS DSVA designs. It shows that the proposed DSVA design has better performance and size than the recently reported on-chip CMOS antenna designs.

#### IV. CONCLUSION

A compact, high-performance 60 GHz DSVA using standard 0.18 µm CMOS technology has been designed and characterized. The antenna, measuring 870 µm × 960 µm, was optimized through simulations and fabricated for experimental validation. It significantly enhanced its radiation performance by incorporating key design features, including a CPW power divider, double-Y balun, corrugations along the flare edges, and a planar arc reflector. Simulation results demonstrated an end-fire radiation pattern with a peak gain of + 0.4 dBi and a radiation efficiency of 38% at 60 GHz. Moreover, the measured impedance bandwidth extended from 50 to 70 GHz, confirming the antenna's wideband operation. The improvement in performance compared to SSVA is attributed to the doubleslot structure, which creates a more uniform aperture field distribution, leading to higher gain. The proposed DSVA design outperforms previously reported on-chip 60 GHz antennas, making it a promising solution for compact, highperformance millimeter-wave.

**Conflicts of Interest:** The authors declare no conflict of interest.

Fig. 12. Simulated 3-D pattern for DSVA at 60 GHz.

Fig. 13. Chip photo of the fabricated DSVA.

Fig. 14. Comparison between the simulated and measured reflection coefficient of the proposed DSVA.

Journal of Engineering Research (JER)

©Tanta University, Faculty of Engineering

ISSN: 2356-9441

Vol. 8 - No. 4, 2024

eISSN: 2735-4873

Table II: Performance comparison of 0.18  $\mu m$  CMOS DSVA with previously reported on-chip CMOS antennas.

| Reference | Antenna Type           | CMOS<br>Process | Area<br>(mm²)      | Frequency<br>(GHz) | Gain<br>(dBi)       | Efficiency<br>(%) |

|-----------|------------------------|-----------------|--------------------|--------------------|---------------------|-------------------|

| [16]      | Vivaldi                | 0.18 µm         | 0.7 × 0.94         | 60                 | - 1.9<br>Simulated  | 24                |

| [15]      | Vivaldi                | 65 nm           | 1.73 × 1.75        | 60                 | - 3<br>Simulated    | N/A               |

| [17]      | Vivaldi                | 0.18 µm         | $0.78 \times 0.93$ | 60                 | - 0.4<br>Simulated  | 32                |

| [8]       | Monopole               | 0.18 µm         | 1.2 × 1.2          | 60                 | - 2.64<br>Simulated | N/A               |

| [23]      | Monopole               | Bi- CMOS        | N/A                | 57                 | - 2.32<br>Simulated | 21                |

| [5]       | Yagi                   | 0.18 µm         | 1 × 0.87           | 60                 | - 0.74<br>Simulated | 21.4              |

| [24]      | Triangular<br>monopole | 0.18 μm         | 1.2 × 1.2          | 64                 | - 0.4<br>Simulated  | 40.9              |

| [9]       | Slot monopole          | 0.18 µm         | 1.2 × 1.2          | 72                 | - 6.3<br>Simulated  | 22                |

| [25]      | Bowtie Slot            | 0.13 μm         | 1 × 1              | 84                 | - 0.58<br>Measured  | N/A               |

| [26]      | Monopole               | 130 nm          | $0.36 \times 0.19$ | 85                 | - 0.35<br>Measured  | N/A               |

| [10]      | Folded dipole          | 65 nm           | $4.7 \times 2.87$  | 94                 | - 1.4<br>Measured   | 60                |

| [13]      | Vivaldi                | 0.18 μm         | 1.2 × 1.2          | 100                | - 4<br>Measured     | 17.7              |

| This work | Vivaldi                | 0.18 µm         | $0.87 \times 0.96$ | 60                 | + 0.4<br>Simulated  | 38 %              |

#### **REFERENCES**

- [1] S. Kumar, A. S. Dixit, R. R. Malekar, H. D. Raut, and L. K. Shevada, "Fifth generation antennas: A comprehensive review of design and performance enhancement techniques," *IEEE Access*, vol. 8, pp. 163568-163593, 2020.

- [2] H. M. Cheema, A. Shamim, and F. Khalid, "Antenna-on-Chip: Design, Challenges, and Opportunities," 2021.

- [3] E. Elsaidy, A. Barakat, A. B. Abdel-Rahman, A. Allam, and R. K. Pokharel, "Ultracompact CMOS 60-GHz tapped-line combline BPF with two transmission zeros using defected ground structures," *IEEE Transactions on Components, Packaging and Manufacturing Technology,* vol. 8, no. 9, pp. 1642-1649, 2018.

- [4] R. Karim, A. Iftikhar, B. Ijaz, and I. B. Mabrouk, "The potentials, challenges, and future directions of on-chip-antennas for emerging wireless applications—A comprehensive survey," *IEEE Access*, vol. 7, pp. 173897-173934, 2019.

- [5] E. Elsaidy, A. Barakat, A. B. Abdel-Rahman, A. Allam, and R. K. Pokharel, "Radiation performance enhancement of a 60 GHz CMOS Quasi-Yagi antenna," in 2016 IEEE 17th Annual Wireless and Microwave Technology

- Conference (WAMICON), 2016: IEEE, pp. 1-4.

- [6] R. Wu *et al.*, "A 60-GHz efficiency-enhanced on-chip dipole antenna using helium-3 ion implantation process," in *2014 44th European microwave conference*, 2014: IEEE, pp. 108-111.

- [7] I. Papapolymerou, R. F. Drayton, and L. P. Katehi, "Micromachined patch antennas," *IEEE Transactions on Antennas and Propagation*, vol. 46, no. 2, pp. 275-283, 1998.

- [8] M.-A. Chung, Y.-H. Chen, and I.-P. Meiy, "Antenna-on-Chip for Millimeter Wave Applications Using CMOS Process Technology," in *Telecom*, 2023, vol. 4, no. 1: MDPI, pp. 146-164.

- [9] M.-A. Chung, C.-C. Hsu, S.-R. Huang, and P.-R. Huang, "A 0.18 μm CMOS Millimeter Wave Antenna-on-Chip with Artificial Magnetic Conductor Design," *Inventions*, vol. 8, no. 3, p. 78, 2023.

- [10] M. Nafe, A. Syed, and A. Shamim, "Gainenhanced on-chip folded dipole antenna utilizing artificial magnetic conductor at 94 GHz," *IEEE Antennas and Wireless Propagation Letters*, vol. 16, pp. 2844-2847, 2017.

- [11] A. Barakat, A. Allam, H. Elsadek, H. Kanaya, and R. K. Pokharel, "Small size 60 GHz

## Journal of Engineering Research (JER) ©Tanta University, Faculty of Engineering

Junior R

ISSN: 2356-9441

Vol. 8 - No. 4, 2024

eISSN: 2735-4873

- CMOS antenna-on-chip: Gain and efficiency enhancement using asymmetric artificial magnetic conductor," in 2014 44th European Microwave Conference, 2014: IEEE, pp. 104-107.

- [12] P. K. Jaiswal, R. Bhattacharya, and A. Kumar, "A UWB antipodal Vivaldi antenna with high gain using metasurface and notches," *AEU-International Journal of Electronics and Communications*, vol. 159, p. 154473, 2023.

- [13] M.-A. Chung, C.-W. Ting, and K.-C. Tseng, "A Wide Bandwidth Vivaldi Antenna Suitable for 5G/6G Communication Utilizing a CMOS 0.18 μm Process," in *Telecom*, 2024, vol. 5, no. 2: MDPI, pp. 400-415.

- [14] K. Sultan. M. Basha, H. Abdullah. Abdallah, and H. El-Hennawy, "A 60-GHz CMOS Quasi-Yagi antenna with enhanced radiation properties," in 12th European Conference and on Antennas Propagation (EuCAP 2018), 2018: IET, pp. 1-3.

- [15] F. A. Ghaffar, L. Roy, and A. Shamim, "A wideband fully planar vivaldi antenna **WPAN** applications," in 2018 18th International Symposium onAntenna Technology Applied Electromagnetics and (ANTEM), 2018: IEEE, pp. 1-3.

- [16] A. S. Abd El-Hameed, A. Barakat, A. B. Abdel-Rahman, A. Allam, and R. K. Pokharel, "A60-GHz double-Y balun-fed on-chip Vivaldi antenna with improved gain," in 2015 27th International Conference on Microelectronics (ICM), 2015: IEEE, pp. 307-310

- [17] A. S. Abd El-Hameed, N. Mahmoud, A. Barakat, A. B. Abdel-Rahman, A. Allam, and R. K. Pokharel, "A 60-GHz on-chip tapered slot Vivaldi antenna with improved radiation characteristics," in 2016 10th European Conference on Antennas and Propagation (EuCAP), 2016: IEEE, pp. 1-5.

- [18] V. TrifunoviC and B. JokanoviC, "Review of printed Marchand and double Y baluns: Characteristics and application," *IEEE* Transactions Microwave Theory onand Techniques, vol. 42, no. 8, pp. 1454-1462,

- [19] L. Fan and K. Chang, "Uniplanar power dividers using coupled CPW and asymmetrical CPS for MICs and MMICs," *IEEE Transactions on Microwave Theory and Techniques*, vol. 44, no. 12, pp. 2411-2420, 1996.

- [20] K.-P. Ma, Y. Qian, and T. Itoh, "Analysis and applications of a new CPW-slotline transition," *IEEE Transactions on Microwave theory and Techniques*, vol. 47, no. 4, pp. 426-432, 1999.

- [21] D. Hua, X.-p. Liao, and H.-c. Liu, "A micro compact coplanar power divider at X-band with finite-width ground plane based on GaAs MMIC technology," *Microsystem technologies*, vol. 19, pp. 1973-1980, 2013.

- [22] G. Kumar Pandey and M. Kumar Meshram, "A printed high gain UWB Vivaldi antenna design using tapered corrugation and grating elements," *International Journal of RF and Microwave Computer-Aided Engineering*, vol. 25, no. 7, pp. 610-618, 2015.

- [23] Q. Liu, A. van den Biggelaar, U. Johannsen, M. C. van Beurden, and A. B. Smolders, "Onchip metal tiling for improving grounded mm-Wave antenna-on-chip performance in standard low-cost packaging," *IEEE Transactions on Antennas and Propagation*, vol. 68, no. 4, pp. 2638-2645, 2019.

- [24] M.-A. Chung, S.-R. Huang, and P.-R. Huang, "Designed on 0.18 µm CMOS Process Small Size Broadband Millimeter Wave Chip Antenna," *Inventions*, vol. 8, no. 3, p. 64, 2023.

- [25] M. S. Khan, F. A. Tahir, A. Meredov, A. Shamim, and H. M. Cheema, "A W-band EBG-backed double-rhomboid bowtie-slot on-chip antenna," *IEEE Antennas and Wireless Propagation Letters*, vol. 18, no. 5, pp. 1046-1050, 2019.

- [26] L. Wu, J. Huang, B. Sun, H. Chang, S. Huang, and H. Liu, "Miniaturized broadband monopole antenna in 130nm CMOS with gain improvement," *IEICE Electronics Express*, vol. 19, no. 8, pp. 20220076-20220076, 2022.